PART7반도체 기본회로

실험 8 :FET 특성

이론

전계효과 트렌지스터(Field Effect Transistor)는 트랜지스터와 함께 증폭, 발진, 스위칭 등을 할 수 있는 반도체 소자로 일반적으로 BJT에 비하여 열잡음이 작고 높은 입출력 임피던스를 갖는 전압 제어형 소자이고, 다수 캐리어의 이동에만 의존하는 단극성 소자로서 제조과정이 간단하며, 집적도를 아주 높게 할 수 있다. FET는 구조상 접합성 FET(Junction FET : JFET)와 절연게이트형 FET(Insulated Gate FET : IGFET 또는 Metal - Oxide -semicond - uctor FET : MOSFET)의 두 종류로 나뉜다.

(1) JFET의 구조 및 특성

그림에서와 같이 JFET의 구조는 반도체의 긴 육면체 양끝이 소스(source)와 그레인(drain)이고, 이 반도체의 중간에서 pn 접합을 이루고 있는 게이트(gate)라는 단자로 되어있다. 이 중 소스와 드레인 사이의 긴 통로를 채널(channel)이라 하며, 따라서 n채널 JFET와 p 채널 JFET로 만들 수 있는데, 본 실험에서는 n체널 JFET에 대해 다루기로 한다.

J-FET와 쌍극성 트랜지스터에서 게이트와 베이스, 드레인과 콜렉터, 그리고 소스와 이미터 사이에는 개략적인 유사성이 나타난다. 그러나 J-FET에서의 전기전도는 게이트-소스접합에 대한 역방향바이어스 전압에 의하여 제어되며, 이에 따라 전계가 발생한다.

쌍극성 트랜지스터의 전도제어는 순방향바이어스된 베이스-이미터접합에서의 베이스전류에 의하여 이루어진다. 이러한 것은 J-FET의 입력(게이트)이 역방향 바이어스된 접합이므로, J-FET의 높은 입력임피던스에 대한 설명이 되는 것이다.

그림 7-32은 드레인 전류 ID대 드레인-소스 사이의 전압 VDS의 특성곡선을 나타낸 것이다. 바이어스 전압, 즉 게이트-소스 사이의 전압 VGS는 이 경우 “0”이 된다. “0”에서 A까지의 첫 번째 영역, 즉 저항성영역(ohmic region)에서 J-FET는 보통의 저항과 같이 동작한다.

전류는 인가전압이 증가함에 따라 선형적으로 증가한다. 이러한 동작은 핀치오프 (pinch-off)영역이 시작될 때까지 대략 1V에서 3V 범위 내에서 발생한다. 이 범위에서(A에서 B까지) 게이트와 채널간의 pn접합에 대한 역방향바이어스가 공핍영역 (depletion region)의 원인이 된다. 핀치오프영역에 도달하기 위하여 역방향바이어스가 충분히 커질 때까지 공핍층은 서로 맞닿을 수 있을 만큼 충분히 넓혀지지 않는다. 두 층이 서로 맞닿을 수 있게끔 충분히 바이어스가 가해졌을 때, 채널에서는 전하가 결핍되어 핀치오프가 된다. 핀치오프는 VDS의 광범위한 변화에 대하여 전류의 흐름이 거의 일정한 영역을 말한다.

그림 7-32에 따르면 A에서 B까지의 이 영역에서 곡선은 거의 수평을 이룬다. 채널의 폭이 0으로 감소됨에 따라 전류의 흐름이 감소되려는 경향이 있으며, 이는 채널을 따라서 전압의 기울기를 완화시키는 원인이 된다. 이러한 것은 공핍영역의 폭을 감소시키며, 이는 전류가 증가하게 되는 원인이 된다. 이 마지막 결과는 전류의 안정된 값이 되며, 평형상태에 이르게 된다.

(2) MOSFET의 구조 및 특성

MOSFET의 게이트는 매우 작고 뛰어난 특성을 갖는 커패시터이며, 채널을 통한 전도는 게이트와 소스 사이에 인가된 전압에 의하여 제어된다. 그러므로 MOSFET의 입력전류는 J-FET에 비한다면 입력전류와 대립이 되는 커패시터의 누설전류로서, 이는 역방향바이어스된 pn접합의 누설전류이다. 따라서 MOSFET의 입력임피던스는 J-FET에 비하여 수십 배 또는 그 이상의 큰 값을 갖는다.

MOSFET의 Gate는 절연물질의 SiO2층을 채널전면에 걸쳐서 침착시키는데 이러한 얇은 SiO2층 위에 금속물질이 놓이게 된다. 그림 7-34은 대표적인 MOSFET의 구조형태를 보인 것이다.

MOSFET의 동작 특성으로는 세부적인 구조에 따라 구분되는 공핍형(depletion-mode)이나 증가형(enhancement- mode)이 있다. 그림 7-35 (a)는 n채널 MOSFET의 특성을 나타낸 것이다. 공핍형에서 채널은 정상적으로 도체이며, 이 때문에 J-FET에서와 같이 전류의 흐름이 감소될 수도 있고, 충분한 게이트전압이 인가됨에 의하여 차단까지도 가능하다. 증가형에서는 채널이 정상적으로 차단상태이며, 게이트전압을 인가함에 따라 줄이거나 또는 늘릴(증가) 수 있으며, 제어할 수가 있게 된다. 공핍형 MOSFET는 그림 (d)에 나타낸 것처럼 증가형에서도 동작할 수 있다.

게이트의 정전용량은 매우 작으며, 따라서 입력임피던스는 매우 높다. 그래서 게이트는 어떤 전압레벨 이상에서 매우 쉽게 하전될 수 있으므로, 커패시터의 좁은 SiO2유전체가 파괴될 수 있다. 대략 50V정도의 전압으로 파괴되며, 이는 정상적인 취급에 따라 발생하는 정전하들에 의하여 쉽게 유도될 수 있음을 의미한다. 이러한 이유 때문에 이들 소자들은 리이드들을 서로 단락시켜서 흔히 패키지화 한다.

게이트와 드레인 사이 및 게이트와 소스 사이의 고유의 정전용량(고주파응답을 제한)은 대체로 MOSFET에서 더 낮으므로, 일반적으로 고주파응답이 JFET에 비하여 더욱 좋다. JFET가 온도에 따라 지수적으로 증가하는 입력누설전류를 갖는데 반하여, MOSFET에서는 온도의 영향이 최소가 된다. MOSFET는 오늘날 보편적으로 이용할 수 있는 온도의 영향을 적게 받는 반도체소자이다.

실험 과정

1. J-FET의 특성을 실험하기 위해 M07의 block e를 사용하여 그림 7-36 회로와 같이 결선하고 각각의 전원을 공급한다.

- VR5는 게이트와 소스 간의 전압인 VGS를 -0~-15V로 변화하기 위해 사용한다.

- VR6는 드레인과 소스 간의 전압인 VDS를 0~15V로 변화하기 위해 사용한다.

2. VR5의 가변 저항값을 좌측으로 돌려 VGS 값이 0이 되도록 한다.

3. 전압계를 사용하여 FET의 D와 S 단자에 각각 연결을 하고 VR6를 돌려 VDS가 1V가 되도록 하고, 전류계에 나타나는 드레인 전류값을 표 7-13해당란에 기록한다.

4. 표 7-13의 VDS가 되도록 VR6를 조정하여 드레인 전류값을 해당란에 기록한다.

5. VR5의 값을 돌려 VGS가 각각 –0.25V, -0.5V, -0,75V가 되도록 하고 표7-13의 VDS 값에 대한 드레인 전류를 위 과정 3) 4)와 같이 수행하여 측정 기록한다.

tab1실험 7-8.1 JFET 특성 측정 (M07의 block e에서 그림 7-36와 같이 회로를 구성한다.)

1.결선방법(M07의 block e)

1.회로 결선

block e의 FET S 단자와 접지단자 간을 황색선으로 연결한다.

block e의 R13 위 단자와 FET G 단자 간을 황색선으로 연결한다.

2.전원 결선

M07 보드의 좌측 Fixed Power의 +15V 단자와 block e의 V+ 단자 간을 적색선으로 연결한다.

M07 보드의 좌측 Fixed Power의 -15V 단자와 block e의 V- 단자 간을 적색선으로 연결한다.

M07 보드의 좌측 Fixed Power의 GND 단자와 접지단자 간을 흑색선으로 연결한다.

3.계측기 결선

전류계 결선

별도의 Digital Multimeter의 전류 측정 기능을 사용하여 측정한다.

드레인에 흐르는 전류(ID) 측정 : block e의 R14 위 단자와 Digital Multimeter의 적색 리드선을 연결하고, FET G 단자에 흑색 리드선을 연결한다.

전압계 결선

VGS 전압측정 : block e에서 FET G 단자와 Signal Input CH A의 A+ 단자 간을 적색선으로 연결하고, 접지단자와 A- 단자 간을 흑색선으로 연결한다.

VDS 전압측정 : block e에서 FET D 단자와 Signal Input CH B의 B+ 단자 간을 적색선으로 연결하고, 접지단자와 B- 단자 간을 흑색선으로 연결한다.

2.결선도

3.측정방법

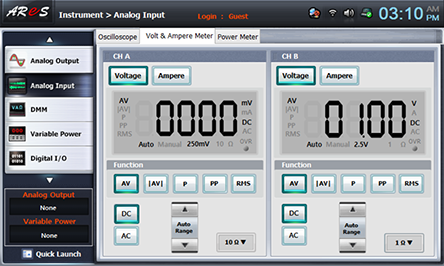

- 1Touch LCD 패널에서 좌측 메뉴에서 analog input을 선택하고, Volt & Ampere Meter 탭을 선택한 다음, CH A, CH B에서 , , 를 클릭한다.

- 2VR5를 조정하여 CH A의 지시값(VGS 전압)이 0.0V가 되도록 한다.

- 3VR6를 조정하여 CH B의 지시값(VDS 전압)이 1.0V가 되도록 한다.

별도의 디지털 멀티미터에서 지시하는 드레인 전류(ID)를 표 7-13 해당란에 기록한다.

표 7-13의 각각의 VDS가 되도록 VR6를 조정하면서 드레인 전류(ID)를 반복 측정하여 해당란에 기록한다.

- 4VR5를 조정하여 CH A의 지시값(VGS 전압)이 –0.25V, -0.50V, -0.75V 일 때 각각 위 과정 3)을 수행하여 측정 기록한다.

실험 결과 보고서

1. 실험 결과표

2. 검토 및 정리

1) 표 7-13 측정값을 가지고 아래 그래프를 그리시오.

2) Graph와 표 7-13에서 VGS = 0V 일 때 동적 드레인 저항을 구하시오.

3) 표 7-13에서 VGS = 0V 일 때 정적 드레인 저항을 구하시오.

4) 동적 드레인 저항과 정적 드레인 저항의 차이점은 무엇인가 기술하시오.

5) 전달 컨덕턴스(transcoductance) g fs는 VGS의 변화에 대한 드레인 전류의 변화로써 측정되어진다. 표 7-13에서 –0.1V에서 –0.2V 까지의 VGS 변화에 대한 전달 컨덕턴스를 구하시오.