PART7Basic Circuit of Semiconductor

Experiment 8 :Characteristic of FET

Theory

FET(Field Effect Transistor) is a semiconductor element that can execute amplification, oscillation and switching with the transistor. This is a voltage control type element that has smaller thermal noise and higher input/output impedance compared to BJT, and also a unipolar element that depends on the movement of a number of carriers. Its manufacturing process is simple and its degree of integration can be very high. By the structure, FET can be categorized as junction FET(JFET) and insulated gate FET(IGFET or Metal-Oxide-Semiconductor FET: MOSFET).

(1) Structure and Characteristic of JFET

As in the fig., JFET is a long hexahedron semiconductor whose both ends are source and grain, and in the middle is gate terminal of pn junction. The long path between the source and the train is channel so JFET can be composed as n channel JFET and p channel JFET, and this experiment will deal with n channel JFET.

(a) Structure of n CH JFET (b) Symbol of JFET and polarity of voltage

(a) When VDS < VP (b) When VDS=VP

(c) When VDS < VP (d) Characteristic of Drain Current -Voltage

In J-FET and bipolar transistor, there are broad similarities between gate and base, drain and collector, and source and emitter. However, the electrical conduction at J-FET is controlled by reverse bias voltage to gate-source junction, and electrical field is generated as a result.

The conduction control of bipolar transistor is executed by base current at base-emitter junction that is forward biased. This could explain high input impedance of J-FET because the input(gate) of J-FET is a reverse biased junction.

Fig.7-32 shows the characteristic curve between drain current ID versus voltage VDS between drain and source. In this case, bias voltage, that is, the voltage between gate and source, VGS is “0”. In the first region from “0” to A, that is, in the ohmic region, J-FET operates just as ordinary resistance.

The current increase linearly as the applied voltage increases. This operation occurs between 1V and 3V range till pinch-off region begins. Within this range(from A to B), the reverse bias to p-n junction between gate and channel is the cause of depletion region. Till the reverse bias becomes big enough to reach pinch-off region, the depletion region does not widen enough to meet each other. When the bias is applied enough so that two regions meet each other, electric charge is depleted in the channel and pinch-off occurs. Pinch-off means the region where the flow of current is almost constant though VDS changes radically.

According to fig.7-32, in the region between A and B, the curve becomes almost horizontal. As the width of channel decreases to 0, the current tends to decrease, and this causes the incline of voltage to be eased following the channel. This reduces the width of depletion region and increases the current. The final value becomes stable value of current and it reaches equilibrium.

(2) Structure and Characteristic of MOSFET

The gate of MOSFET is a capacitor that is very small and excellent, and the voltage applied between the gate and the source controls the conductance through channel. Therefore, compared to that of J-FET, the input current of MOSFET is the leakage current of capacitor which conflicts to the input current, and is also the leakage current of reverse biased p-n junction. Therefore, input impedance of MOSFET is dozens times bigger than that of J-FET.

The gate of MOSFET deposits SiO2 layer of insulated material on the entire surface of channel, and metal material is put on this thin SiO2 layer. Fig.7-34 shows typical structure of MOSFET. /p>

(a) Depletion-mode (b) Enhancement-mode

- (a) Characteristic of n channel enhancement-mode

- (b) Characteristic of n channel depletion-mode

- (c) Symbol of n channel enhancement-mode

- (d) Symbol of n channel depletion-mode

- (e) Symbol of p channel enhancement-mode

- (f) Symbol of p channel depletion-mode

MOSFET can be categorized by detailed structure as depletion-mode and enhancement-mode. Fig.7-35(a) shows the characteristic of n channel MOSFET. In depletion mode, the channel is a normal conductor so as in J-FET the current flow can be decreased or cutoff by applying enough gate voltage. In enhancement mode, the channel is normally cut off but it can be increased or decreased and controlled by applying gate voltage. Depletion mode MOSFET can be operated in enhancement mode as in fig.(d).

The electrostatic capacity of gate is very small so the input impedance is very high. Therefore, the gate can be easily charged over certain voltage level and the narrow SiO2 dielectric of capacitor can be damaged. The voltage of about 50V can damage it, and this means that it can be induced by electric charges generated by normal treatment. With these reasons, these elements short the leads and make them as packages.

The inherent electrostatic capacitance between gate and drain, and between gate and source(deducting high frequency response) is generally lower at MOSFET so the high frequency response is normally better than JFET. While JFET has input leakage current that increases exponentially according to temperature, the effect of temperature is minimum with MOSFET. MOSFET is a semiconductor element which can be commonly used and which is hardly affected by temperature.

Experiment Process

1. To experiment the characteristic of J-FET, make a connection as in fig.7-36 using Block e of M07 and supply each power.

- VR5 is used to change VGS, the voltage between gate and source, as -0~-15V.

- VR6 is used to change VDS, the voltage between drain and source, as 0~15V.

2. Turn the variable resistance of VR5 to the left and makethe value of VGS as 0.

3. Connect to D and S terminals of FET each using the voltmeter, turn VR6 to make VDS as 1V, and record the drain current value indicated at the ammeter in the relevant column of table 7-13.

4. Adjust VR6 so that it becomes VDS of table 7-13 and record the drain current value in the relavant column.

5. Turn VR5 to make VGS as 0.25V, -0.5V, -0,75V, execute as 3), 4) processes above and measure and record the drain current value to the value of VDS in table 7-13.

tab1Experiment 7-8.1 JFET Characteristic Measurement (In Block e of M07, compose a circuit as in fig.7-36.)

1.Connection(Block e of M07)

1.Circuit Connection

Connect between FET S terminal of Block e and the earthing terminal with yellow line.

Connect between upper terminal of R13 of Block e and FET G terminal with yellow line.

2.Power Connection

Connect between +15 terminal of Fixed Power on the left of M07 board and V+ terminal of Block e with red line.

Connect between -15 terminal of Fixed Power on the left of M07 board and V- terminal of Block e with red line.

Connect between GND terminal of Fixed Power on the left of M07 board and the earthing terminal with black line.

3.Measuring Instrument Connection

Ammeter Connection

Measure by using the current measurement function of separate Digital Multimeter.

Measuring the current(ID) flowing on the drain: Connect the red lead wire of Digital Multimeter to upper terminal of R14of Block e and the black line to FET G terminal.

Voltmeter Connection

Measuring the voltage VGS: In Block e, connect between FET G terminal and A+ terminal of Signal Input CH A with red line, and between earthing terminal and A- terminal with black line.

Measuring the voltage VDS: In Block e, connect between FET D terminal and B+ terminal of Signal Input CH B with red line, and between earthing terminal and B- terminal with black line.

2.Wiring Diagram

3.Measurement

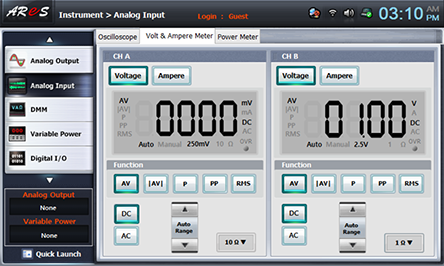

- 1Choose analog input at left menu of Touch LCD panel, click Volt & Ampere Meter and click , , for CH A and CH B each.

- 2Adjust VR5 to make the value indicated at CH A(VGS voltage) as 0.0V.

- 3Adjust VR6 to make the value indicated at CH B(VDS voltage) as 1.0V.

Record the drain current (ID) indicated at the separate digital multimeter in the relevant column of table 7-13.

Adjust VR6 so that it becomes VDS of table 7-13 and measure the drain current(ID) repeatedly and record the result in the relevant column.

- 4Adjust VR5 and execute 3) process above when the value indicated atCH A(VGS voltage) is–0.25V, -0.50V, -0.75V and measure and record the result.

Experiment Result Report

1. Experiment Result Table

2. Review and Explanation

1) Draw the graph below with the measured value of table 7-13.

2) When VGS = 0V, calculate the dynamic drain resistance in the graph and table 7-13.

3) When VGS = 0V, calculate the static drain resistance in table 7-13.

4) Explain the difference between dynamic drain resistance and static drain resistance.

5) The transconductance gfs can be measured as the change of drain current to the change of VGS. In table 7-13, calculate the transconductance to the change of VGS from -0.1V to -0.2V.